# CRYSTAL OSCILLATOR DESIGN AND TEMPERATURE COMPENSATION

Marvin E. Frerking

# CRYSTAL OSCILLATOR DESIGN AND TEMPERATURE COMPENSATION

Marvin E. Frerking

The author assumes no responsibility for the use of any circuitry, program, or technique contained in this publication nor is any patent license implied.

Van Nostrand Reinhold Company International Offices: London Toronto Melbourne

Copyright © 1978 by Litton Educational Publishing, Inc.

Library of Congress Catalog Card Number: 77-17876

ISBN: 0-442-22459-1

All rights reserved. No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means-graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems-without permission of the publisher.

Manufactured in the United States of America

Published by Van Nostrand Reinhold Company 135 West 50th Street, New York, N.Y. 10019 Published simultaneously in Canada by Van Nostrand Reinhold Ltd.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

## Library of Congress Cataloging in Publication Data

Frerking, Marvin E

Crystal oscillator design and temperature compensation.

Includes bibliographical references and index.

- 1. Oscillators, Crystal. 2. Oscillators, Transistor.

- 3. Frequency stability. 4. Temperature control.

- I. Title.

TK7862.07F73 621.3815'33

77-17876

ISBN 0-442-22459-1

# **Foreword**

Crystal oscillators have been in use now for well over 50 years—one of the first was built by W. G. Cady in 1921. Today, millions of them are made every year, covering a range of frequencies from a few Kilohertz to several hundred Megahertz and a range of stabilities from a fraction of one percent to a few parts in ten to the thirteenth, with most of them, by far, still in the range of several tens of parts per million. Their major application has long been the stabilization of frequencies in transmitters and receivers, and indeed, the utilization of the frequency spectrum would be in utter chaos, and the communication systems as we know them today unthinkable, without crystal oscillators.

With the need to accommodate ever increasing numbers of users in a limited spectrum space, this traditional application will continue to grow for the foreseeable future, and ever tighter tolerances will have to be met by an ever larger percentage of these devices.

Narrowing the channel spacing—with its concomitant requirements for increasingly more stable carrier frequencies—is but one of the alternatives to increase the number of potential users of the frequency spectrum. Subdividing the time during which a group of users has access to a given channel is another; and many modern radio transmission systems make use of this principle. Here again, the crystal oscillator plays a dominant role; not to control the carrier frequency, but to keep the time slots for the various users coordinated, that is, to serve as the clock rate generator of the systems clocks in transmitters and receivers. The demands on oscillator performance are often even more stringent in this application than for carrier stabilization alone.

The use of crystal oscillators as clock rate generators has seen a rate of growth in the recent past that is nothing short of explosive, with no end in sight yet, in applications that are quite unrelated to the communications field, such as in the quartz wrist watch and in the microprocessor. Other uses include reference standards in frequency counters and time interval meters, gauges for temperature and pressure, and instruments for the measurement of mass changes for scientific and environmental sensing purposes, to name just a few.

In short, the crystal oscillator is now more in demand than ever, and the need for improved performance in mass producible devices becomes more urgent with

nearly every new application. An increasing number of engineers, therefore, find themselves confronted with the challenge of designing crystal oscillators with near optimum performance, as tailored to a specific application. Those new in the field are bound to discover very soon that there is no substitute for a considerable amount of hands-on experience. Rarely can a circuit reported on in the literature be used without modifications, and details, not discussed fully in the descriptions provided, are often found to be significant.

The possible combinations of circuit elements that make a viable oscillator are nearly limitless, and while most experienced designers have gravitated toward a few basic configurations, no one circuit, or even small group of circuits, has as yet evolved that is, in all details, universally suitable. Nor does it appear likely that this will happen in the foreseeable future, if for no other reason than because new active devices are continually being brought to market, with often significant advantages for use in oscillator circuits, but requiring different conditions for proper operation. The general principles of crystal oscillator design, however, remain.

The basic building blocks of a crystal oscillator are the feedback circuit containing the crystal unit; the amplifier containing one or more active devices; and circuitry or devices such as needed for modulation, temperature compensation or control, etc.

What is needed most by the circuit designer is a clear approach to understanding the interrelationship of the various circuit elements within each of these building blocks and of the blocks with one another. And this holds true whether the goal is an oscillator, hand-tailored in small quantities to achieve the highest performance possible, or mass produced and capable of meeting the specified requirements under worst case conditions. While such approaches do exist, their exposition in the literature is scarce. It is to fill this void that Mr. Frerking has written this book.

M. E. Frerking is surely one of the most accomplished and innovative practitioners of the art of crystal oscillator design, with extensive experience in the development of high performance oscillators for high volume use. In his book he shares with the reader the design techniques that he has found most useful and conveys a wealth of practical information that will be of immediate use to engineers who are faced with the challenge of designing a crystal oscillator for today's more demanding applications.

Mr. Frerking's book is a timely, and most welcome, major addition to the literature on crystal oscillators.

Erich Hafner, PHD. Supervisory Research Physicist US Army Electronics Technology & Devices Laboratory Fort Monmouth, NJ

# Acknowledgments

The author wishes to express his sincere appreciation to the Collins Telecommunications Products Division of Rockwell International whose support and facilities made this work possible, and to those engineers working in the field of frequency control whose contributions have resulted in many of the techniques described in this book.

The author would also like to acknowledge the assistance rendered by Dr. John Robinson and Mr. H. Paul Brower for their suggestions and assistance in preparing the manuscript.

# List of Symbols

| Symbol           | Description                                                      |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------|--|--|--|--|--|--|

| $b_f$            | forward transfer susceptance                                     |  |  |  |  |  |  |

| $b_i$            | input susceptance                                                |  |  |  |  |  |  |

| $b_o$            | output susceptance                                               |  |  |  |  |  |  |

| $b_r$            | reverse transfer susceptance                                     |  |  |  |  |  |  |

| $C_0$            | shunt capacity across crystal                                    |  |  |  |  |  |  |

| $C_1$            | motional arm capacitance                                         |  |  |  |  |  |  |

| $f_a$            | antiresonant frequency                                           |  |  |  |  |  |  |

| $f_L$            | frequency at load capacitance $C_L$                              |  |  |  |  |  |  |

| $f_s$            | series resonant frequency                                        |  |  |  |  |  |  |

| $g_f$            | forward transfer conductance                                     |  |  |  |  |  |  |

| $g_f(\min)$      | minimum forward transfer conductance required for oscillation    |  |  |  |  |  |  |

| $g_i$            | input conductance                                                |  |  |  |  |  |  |

| $g_m$            | forward transfer conductance (transconductance)                  |  |  |  |  |  |  |

| $g_o$            | output conductance                                               |  |  |  |  |  |  |

| $g_r$            | reverse transfer conductance                                     |  |  |  |  |  |  |

| $h_f$            | forward current transfer ratio                                   |  |  |  |  |  |  |

| $h_i$            | input impedance                                                  |  |  |  |  |  |  |

| K                | Boltzman's constant $1.38 \times 10^{-23} \mathrm{J/^{\circ} K}$ |  |  |  |  |  |  |

| $L_1$            | motional arm inductance                                          |  |  |  |  |  |  |

| $P_c$            | power dissipated in crystal                                      |  |  |  |  |  |  |

| ppm              | parts per million                                                |  |  |  |  |  |  |

| q                | electron charge 1.602 × 10 <sup>-19</sup> C                      |  |  |  |  |  |  |

| $R_1$            | motional arm resistance                                          |  |  |  |  |  |  |

| $R_e$            | equivalent resistance of crystal                                 |  |  |  |  |  |  |

| $R_{\rm in}$     | parallel input resistance                                        |  |  |  |  |  |  |

| $R_L$            | external load resistance                                         |  |  |  |  |  |  |

| $R_{\text{max}}$ | maximum resistance crystal oscillator is capable of handling     |  |  |  |  |  |  |

# x List of Symbols

| $R_T$       | total resistive component of collector load           |

|-------------|-------------------------------------------------------|

| $\omega_T$  | angular frequency at which the common emitter current |

|             | gain has decreased to unity                           |

| $X_e$       | equivalent reactance of crystal                       |

| $y_f$       | forward transfer admittance                           |

| $y_i$       | input admittance                                      |

| $y_o$       | output admittance                                     |

| $y_r$       | reverse transfer admittance                           |

| $Z_f$       | forward transfer impedance                            |

| $Z_f \ Z_i$ | input impedance                                       |

| $Z_o$       | output impedance                                      |

| $Z_r$       | reverse transfer impedance                            |

# Contents

| Foreword, Erich Hafner | ۱ | V |

|------------------------|---|---|

| List of Symbols / ix   |   |   |

- 1. INTRODUCTION / 1

- 2. BASIC OSCILLATOR THEORY / 3

- 3. METHODS OF DESIGN / 4

- 3.1. Experimental Method of Design / 4

- 3.2. Y-Parameter Method of Design / 5

- 3.3. Power Gain Method of Design / 7

- 3.4. Nonlinear Modifications / 11

## 4. OSCILLATOR FREQUENCY STABILITY / 14

- 4.1. Temperature Effects of Frequency / 14

- 4.1.1. Temperature Control / 15

- 4.1.2. Temperature Compensation / 16

- 4.2. Long-Term Frequency Drift / 16

- 4.3. Short-Term Frequency Stability / 17

# 5. QUARTZ CRYSTAL RESONATORS / 20

- 5.1. Load Capacitance / 25

- 5.2. Pin-To-Pin Capacitance / 25

- 5.3. Resistance / 26

- 5.4. Rated or Test Drive Level / 26

- 5.5. Frequency Stability / 26

- 5.6. Finishing or Calibration Tolerance / 28

- 5.7. Crystal Aging / 29

- 5.8. Q and Stiffness of Crystals / 29

- 5.9. Mechanical Overtone Crystals / 30

- 5.10. Spurious or Unwanted Modes / 31

- 5.11. Vibration, Shock, and Acceleration / 34

- 5.12. Standard Military Crystals / 34

- 5.13. Specifications and Standards / 39

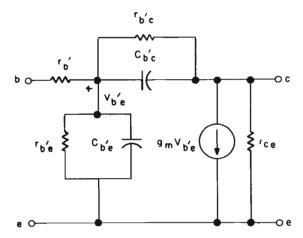

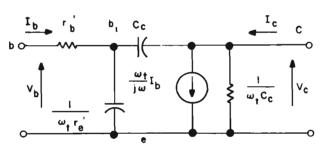

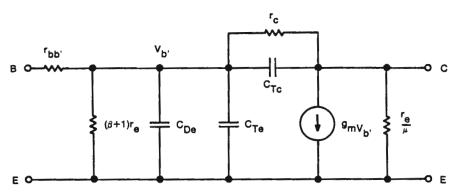

## 6. DISCUSSION OF TRANSISTORS / 40

- 6.1. Transistor Equivalent Circuits / 41

- 6.2. Y-Parameter Model / 42

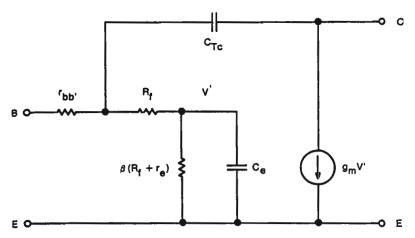

- 6.3. Hybrid  $\pi$  Equivalent Circuit / 44

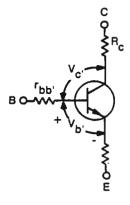

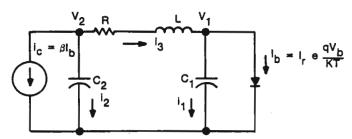

- 6.4. Nonlinear Models / 46

- 6.4.1. Intrinsic Transistor Model / 47

- 6.4.2. Nonlinear Model with Emitter Degeneration / 52

## 7. OSCILLATOR CIRCUITS / 56

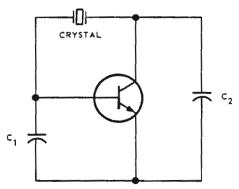

- 7.1. Pierce, Colpitts, and Clapp Oscillators / 56

- 7.2. Pierce Oscillator / 58

- 7.2.1. Small-Signal Analysis / 58

- 7.2.2. Large-Signal Analysis / 63

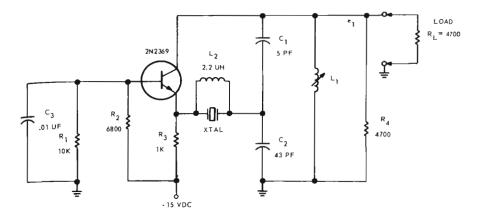

- 7.2.3. 1- to 3-MHz Pierce Oscillator / 66

- 7.2.4. 1- to 10-MHz Pierce Oscillator / 67

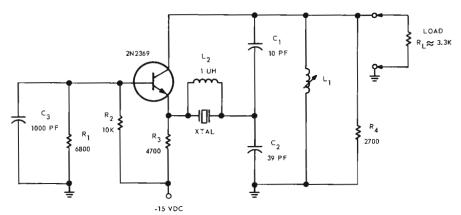

- 7.2.5. 10- to 20-MHz Pierce Oscillator / 69

- 7.2.6. Overtone Pierce Oscillator / 70

- 7.2.7. 25-MHz Pierce Oscillator / 71

- 7.2.8. Impedance-Inverting Pierce Oscillator / 72

- 7.2.9. 25-MHz Impedance-Inverting Pierce Oscillator / 74

- 7.2.10. 50-MHz Impedance-Inverting Pierce Oscillator / 75

- 7.2.11. 75-MHz Impedance-Inverting Pierce Oscillator / 75

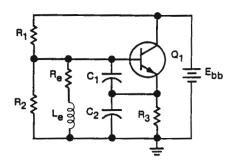

- 7.3. Colpitts Oscillator / 76

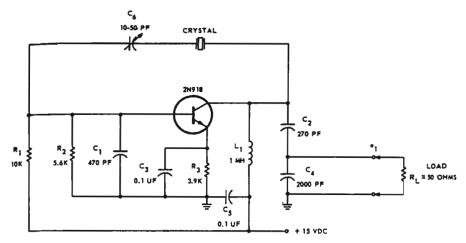

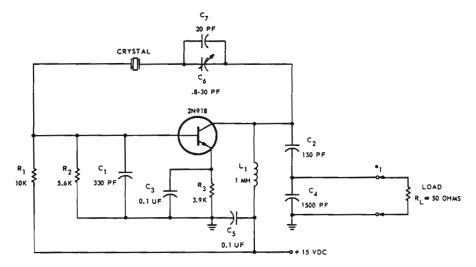

- 7.3.1. 3- to 10-MHz Colpitts Oscillator / 82

- 7.3.2. 10- to 20-MHz Colpitts Oscillator / 83

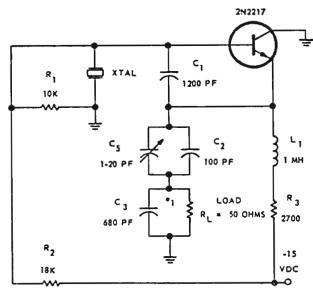

- 7.4. Clapp Oscillator / 85

- 7.4.1. 3- to 20-MHz Clapp Oscillator Circuit / 88

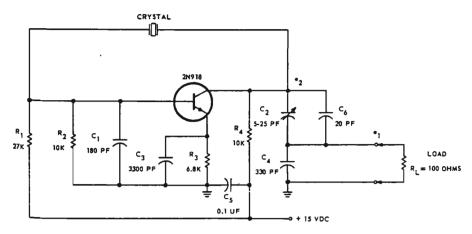

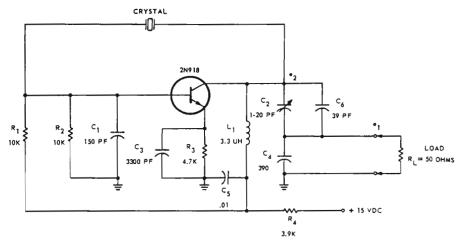

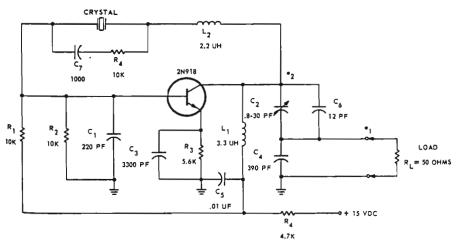

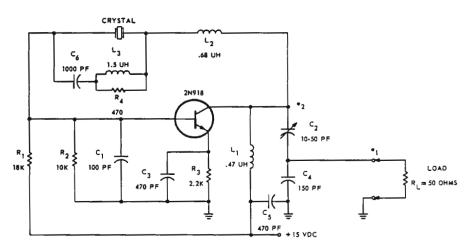

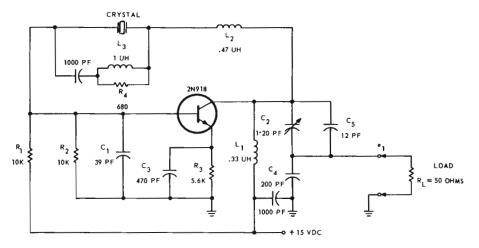

- 7.5. Grounded-Base Oscillator / 89

- 7.5.1. 25-MHz Grounded-Base Oscillator / 95

- 7.5.2. 50-MHz Grounded-Base Oscillator / 96

- 7.5.3. 75-MHz Grounded-Base Oscillator / 98

- 7.5.4. 110-MHz Grounded-Base Oscillator / 99

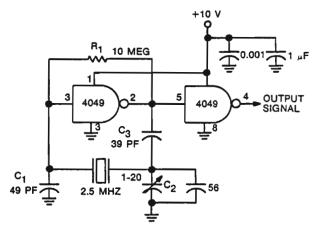

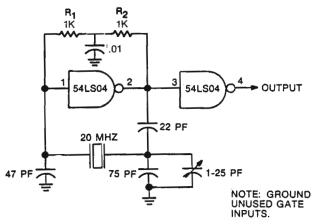

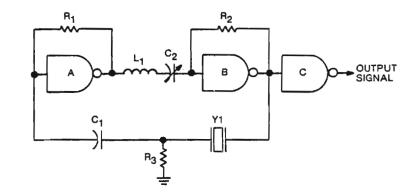

- 7.6. Gate Oscillators / 100

- 7.6.1. Single-Gate Oscillators / 100

- 7.6.2. Multiple-Gate Oscillators / 106

- 7.7. Integrated-Circuit Oscillators / 110

# 8. PREPRODUCTION TESTS FOR CRYSTAL OSCILLATORS / 119

## 9. OTHER TOPICS / 121

- 9.1. Crystal Switches / 121

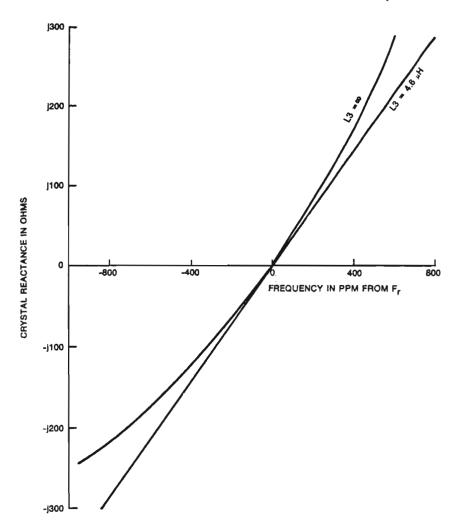

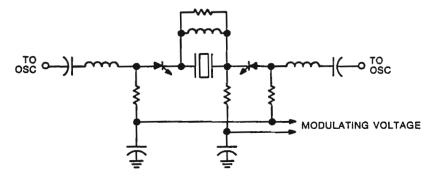

- 9.2. Pullable Oscillators / 122

- 9.3. Crystal Ovens / 126

- 9.4. Squegging, Squelching, or Motorboating / 127

- 9.5. Spurious Oscillations / 128

# 10. TEMPERATURE COMPENSATION / 130

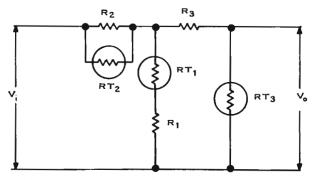

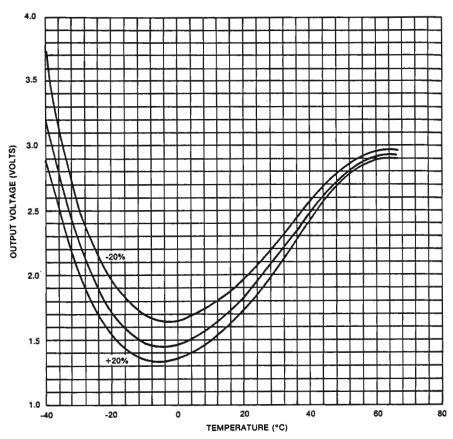

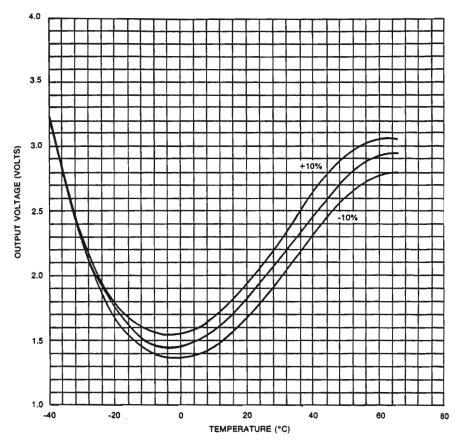

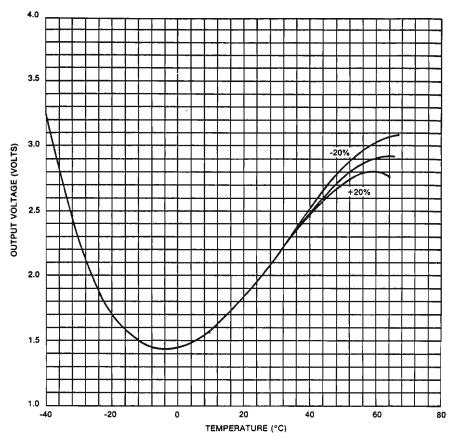

- 10.1. Analog Temperature Compensation / 131

- 10.2. Hybrid Analog-Digital Compensation / 146

- 10.3. Digital Temperature Compensation / 152

- 10.4. Temperature Compensation with Microprocessors / 157

- Appendix A Derivation of the Complex Equation for Oscillation / 177

- Appendix B Derivation of Y-Parameter Equations for the Pierce Oscillator / 180

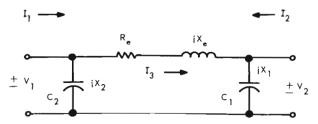

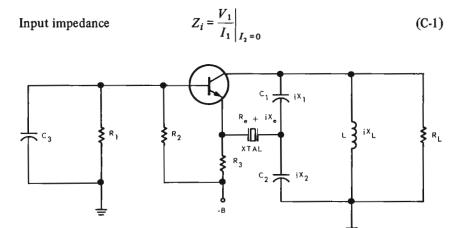

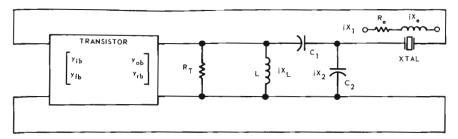

- Appendix C Derivation of Y-Parameter Equations for the Grounded-Base

Oscillator / 188

- Appendix D Derivation of Approximate Equations for the Clapp Oscillator / 193

- Appendix E Derivation of Approximate Equations for the Pierce Oscillator Analysis / 195

- Appendix F Derivation of Approximate Equations for the Colpitts

Oscillator / 197

- Appendix G Large-Signal Transistor Parameters / 199

- Appendix H Large-Signal Transistor Parameters with Emitter

Degeneration / 209

- Appendix I Nonlinear Analysis of the Colpitts Oscillator Based on the Principle of Harmonic Balance / 216

- Appendix J Mathematical Development of the Sideband Level versus

Phase Deviation Equation / 224

- Appendix K Derivation of Crystal Equations / 226

- Appendix L Sample Crystal Specification / 231

Bibliography / 235

INDEX / 239

# CRYSTAL OSCILLATOR DESIGN AND TEMPERATURE COMPENSATION

# **1** Introduction

The increasing demand in radio communications for channel space as well as the use of sophisticated navigation systems and data transmission has resulted in increased frequency stability requirements in many items of equipment. As a result, the demands on crystal oscillators have become more stringent. In many cases, it is no longer sufficient merely to use a crystal oscillator; now it is necessary to take measures to ensure that the crystal oscillator will possess a high degree of frequency stability. Designs of this type are often quite difficult for the engineer who has had little or no prior experience with crystal oscillators; consequently, much of the material in this book is directed to the individual who has a good background in circuit theory but who is not necessarily experienced with crystal oscillator design.

The book deals primarily with transistor oscillators, since nearly all precision oscillators at the present time use discrete transistors. The use of gate oscillators and clock oscillator integrated circuits is widespread in lower stability applications, and these are discussed in Chapter 7.

A practical treatment of quartz crystal resonators is presented in Chapter 5 which gives the designer a good working knowledge of the devices. In Chapter 6, the nonlinear properties of transistors are explored to enable prediction of the amplitude of oscillation and the harmonic content for various oscillators. Chapter 7 then brings together all the information already presented and presents the actual design equations for oscillators covering the entire frequency spectrum from several kHz to 150 MHz. It also includes over 20 tested circuits with component values.

Crystal oscillators, in general, are more critical than most electronic circuits. As such, it behooves the design engineer to take special precautions to ensure that his oscillator circuit will perform

## 2 Crystal Oscillator Design and Temperature Compensation

properly when produced in quantity. Chapter 8 consists of a discussion of several tests which should be conducted to determine with reasonable assurance whether the circuit will perform properly when produced in quantity.

Crystal ovens, discussed briefly in Chapter 9, are used almost exclusively to achieve stabilities better than  $5 \times 10^8$ . The treatment of ovens is limited primarily to a description of the basic techniques and what can be achieved, no attempt is made to give detailed design information.

The spectral purity of crystal oscillators may be an important consideration in some applications and, although not treated in this book, should not be overlooked. The reader is directed to numerous articles in the literature for designs of this type.

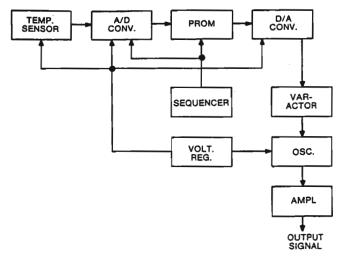

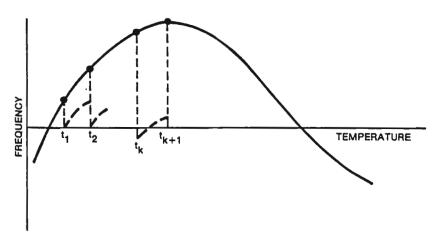

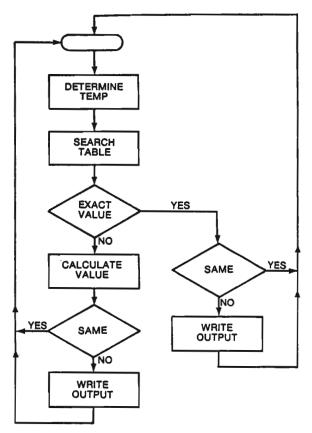

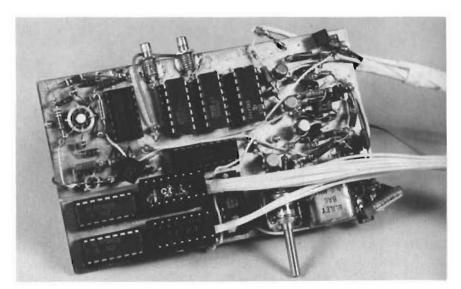

A unique system is presented in Chapter 10, whereby a microprocessor can be used to temperature-compensate a crystal oscillator. This system is compared with three other methods for temperature compensation. Chapter 10 also contains a thorough treatment of temperature compensation in general, which enables the average design engineer to accomplish successful compensation of semiprecision oscillators, improving the stability by as much as two orders of magnitude.

Many of the derivations required to develop the design equations are carried out in the appendices, but the conclusions are presented in the main text. This results in an easily readable volume with the details still available for those interested in probing deeper into the mechanics of the derivations and the assumptions made.

# 2

# **Basic Oscillator Theory**

In undertaking the design of a crystal oscillator, an understanding of hasic oscillator principles is not only desirable but essential. Therefore, a brief explanation of the operation of a crystal oscillator is given here. Basically, a crystal oscillator can be thought of as a closed loop system composed of an amplifier and a feedback network containing the crystal. Amplitude of oscillation builds up to the point where nonlinearities decrease the loop gain to unity. The frequency adjusts itself so that the total phase shift around the loop is 0 or 360 degrees. The crystal, which has a large reactance-frequency slope, is located in the feedback network at a point where it has the maximum influence on the frequency of oscillation. A crystal oscillator is unique in that the impedance of the crystal changes so rapidly with frequency that all other circuit components can be considered to be of constant reactance, this reactance being calculated at the nominal frequency of the crystal. The frequency of oscillation will adjust itself so that the crystal presents a reactance to the circuit which will satisfy the phase requirement. If the circuit is such that a loop gain greater than unity does not exist at a frequency where the phase requirement can be met, oscillation will not occur.

The application of these principles to oscillator design usually is difficult because many factors play an important part in the operation. As a result, the design of transistorized crystal oscillators is often a "cut and try" procedure.

Methods have been developed for predicting the amplitude of oscillation based on the small-signal loop gain. The reduction in gain for a transistor operating at large signal values is predictable and has been plotted as a function of the ac base-to-emitter voltage. Since it is known that the loop gain after equilibrium has been reached will be unity, the reduction factor is numerically equal to the small-signal loop gain. Using this value, the amplitude of oscillation can be predicted from the graphs.

# 3

# Methods of Design

Three methods of design are presented in this book, each of which has its advantages. The first, which is highly experimental, consists of giving a qualitative explanation of how the circuit works and presenting a number of typical schematic diagrams for that oscillator configuration. The second method consists of deriving the equations for oscillation in terms of the Y-parameters of the transistor. The third method consists of measuring the gain and input impedance of the transistor as a function of its load impedance. This information is used to calculate component values for the circuit with relatively simple equations. The amplitude of oscillation can then be predicted using the methods of paragraph 3.4.

## 3.1. EXPERIMENTAL METHOD OF DESIGN

The experimental method of design consists of finding a suitable circuit which can be modified and/or optimized to meet a particular set of requirements. To assist in this design approach, Chapter 7 contains a number of laboratory tested oscillator circuits and a qualitative explanation of their operation. The appropriate circuit type most suited for a particular application can be selected with the aid of Table 7-1. The individual circuits have not been designed or optimized with respect to any particular performance characteristic, but sufficient reserve gain has been provided to allow some modification.

The following precautionary items must be presented in regard to the use or modification of any of these circuits:

a. Since the mechanical arrangement of a circuit usually affects its performance, complete testing of the circuit in accordance with Chapter 8 should be accomplished even though the circuit values presented are used. b. Substitution of transistors or gates for those specified should be within the same basic family and power level. Indiscriminate substitution of active element types may greatly change the performance of a given oscillator circuit.

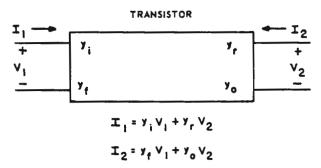

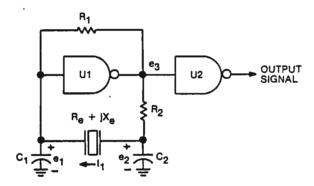

# 3.2. Y-PARAMETER METHOD OF DESIGN

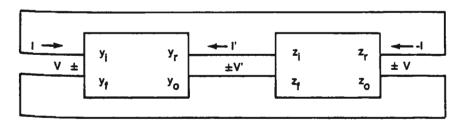

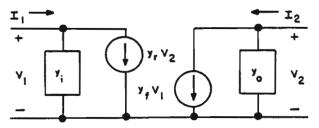

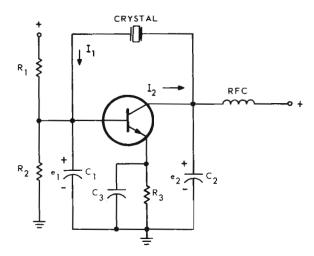

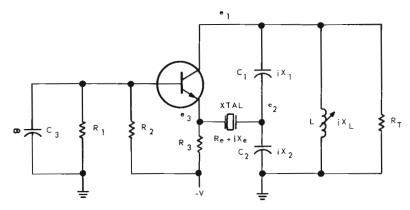

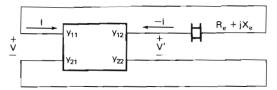

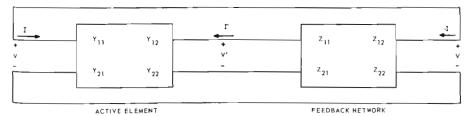

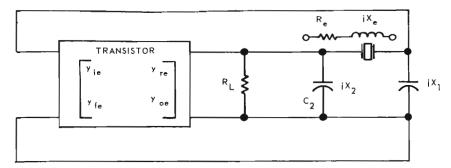

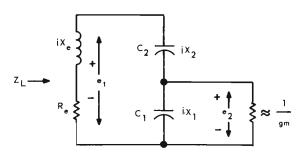

The second approach to oscillator design consists of using the Y-parameters of the transistor (see Chapter 6). The equations for oscillation are derived in the following manner. Using the block diagram of Figure 3-1, the complex equation for oscillation can be shown (see Appendix A) to be:

$$y_f Z_f + y_i Z_o + y_o Z_i + y_r Z_r + \Delta y \Delta Z + 1 = 0,$$

(3-1)

where

$$\Delta y = y_o y_i - y_f y_r$$

,  $\Delta Z = Z_o Z_i - Z_f Z_r$ .

Although any set of parameters may be used for the amplifier and any set for the feedback network, it is convenient to use Y-parameters for the amplifier and Z-parameters for the feedback network. . . . It is important to note that the use of equation (3-1) implies the assumption that the amplifier is a linear circuit. The application of equation (3-1) therefore can yield no information concerning harmonic generation or the limiting of amplitude as the result of dependence of circuit parameters upon amplitude. The assumption that the amplifier is linear is not valid at large amplitudes. At large amplitudes, the Y-parameters therefore must be defined as the ratios of fundamental components of current to fundamental components of voltage!

The equations for specific oscillator types are derived by determining the Z-parameters of the feedback network and substituting them

Figure 3-1. Block diagram of a transistorized crystal oscillator.

into equation (3-1). The complex equation is then separated into real and imaginary parts. The real part generally yields an expression for the transconductance  $g_f$  required for oscillation while the imaginary part yields an expression for the crystal reactance  $X_L$  necessary to satisfy the phase shift requirement. The equations and the assumptions made are presented for the various oscillators in Chapter 7.

Since the equations in general do not give highly accurate results, it is well to use them in connection with the experimental approach (see section 3.1). However, the equations do give an indication of how changing a given component will affect the overall performance and thus are often quite useful. The equations are generally of the form

$$g_f = f_1(a, b, c, d, ...)$$

$X_L = f_2(a, b, c, d, ...),$

where a, b, c, d... represent various components and parameters of the circuit;  $X_L$  is the crystal reactance; and  $g_f$  is the small-signal transconductance required for oscillation to begin. The ratio  $g_f$  (transistor)/ $g_f$  (required) is a measure of the loop gain, which must be greater than unity for oscillations to build up. Generally, if the loop gain is greater than 2 to 3, satisfactory operation results. If limiting

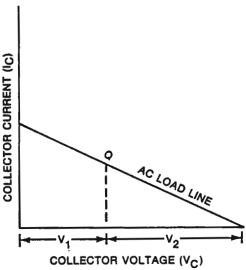

Figure 3-2. Voltage prediction from the Q-point and load line.35

takes place as a result of the base-to-emitter junction being cut off during part of the cycle, the amplitude of oscillation can be predicted using Figure 3-6. Limiting of this type generally results in good frequency stability. The oscillator may be biased to produce collector limiting. If this is the case, the output voltage can be determined by constructing a load line as shown in Figure 3-2. The peak output voltage will be approximately  $V_1$  or  $V_2$ , whichever is smaller. This is a rule of thumb only and not highly accurate.

The oscillator should be designed to require the same crystal reactance  $(X_L)$  as that called out by the crystal specification for onfrequency operation. In the case of series resonant crystals,  $X_L = 0$ .

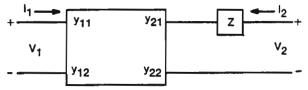

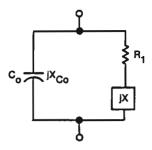

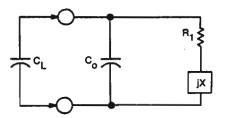

## 3.3. POWER GAIN METHOD OF DESIGN\*

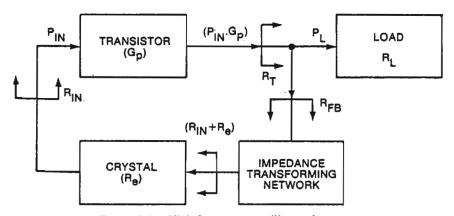

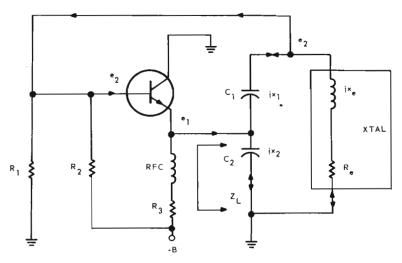

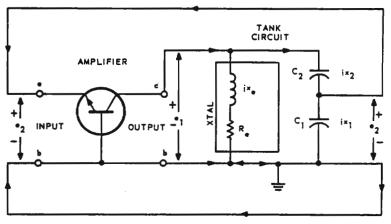

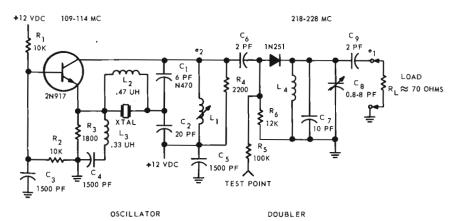

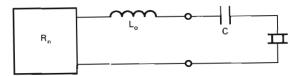

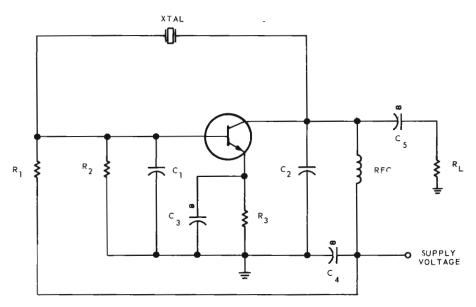

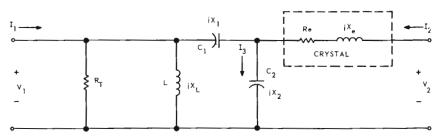

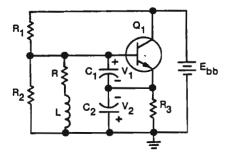

The third approach to oscillator design is basically a power gain analysis. Phase shift considerations are taken care of experimentally by getting the crystal to operate on frequency. The usefulness of this design approach generally is limited to series mode oscillators which can be represented by the block diagram of Figure 3-3.

The power gain required from the transistor must be sufficient to supply the output power, power losses, and the input power required

Figure 3-3. High-frequency oscillator elements.

<sup>\*</sup>The results presented here are essentially a summary of the Power Gain Method of design developed under sponsorship of the US Army Electronics Command, see reference 31.

for the transistor:

$$(P_{\rm in} G_P) = P_L + P_{\rm in} + P_d,$$

(3-2)

where

$P_{\rm in}$  = input power to transistor,

$G_P$  = power gain of transistor,

$P_L$  = output power to an external load, and

$P_d$  = all other power losses within the oscillator circuit.

Using equation (3-2), an oscillator may be designed as follows:

A. Determine the transistor power gain (experimentally).

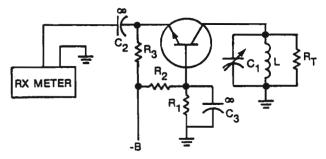

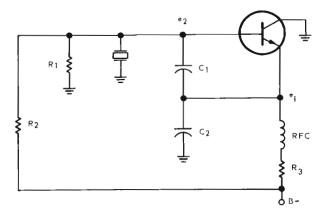

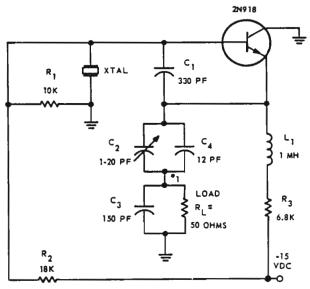

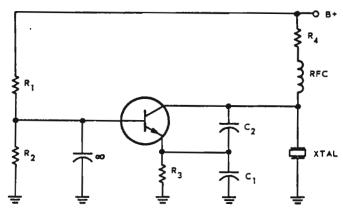

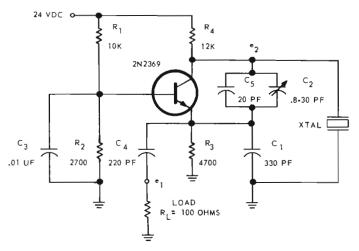

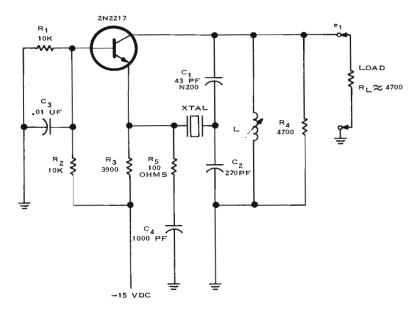

Step 1. Connect the transistor as a single-tuned amplifier in the grounded-base or grounded-emitter configuration, whichever is to be used in the type of oscillator being designed. A circuit similar to that of Figure 3-4 may be used. The circuit should be arranged so that it can be mounted on the impedance measuring device such as a network analyzer or RX meter with the input near the ungrounded terminal. Provisions should be made for connecting RF voltmeters to the input and output of the transistor.

Step 2. Measure the power gain and input impedance as a function of the load resistance  $R_T$ .\*

- (a) For various values of load resistance, determine the power gain and the input impedance, increasing the value of the load resistor at each step until instability occurs.

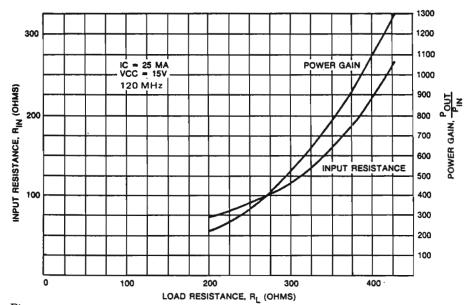

- (b) Plot the power gain and input resistance versus load resistance. A graph similar to that of Figure 3-5 should result.

- (c) From the power gain graph, select a value  $R_T$  giving a gain of 200-300, and note the input resistance  $R_{\rm in}$  at the power gain selected.

B. Calculate the feedback network. Power gain values determined in A include all circuit losses that will be present in the oscillator

<sup>\*</sup>The maximum input voltage that can be applied to the transistor before nonlinearity occurs is about 10 mV. Since the output of the Boonton RX meter is about 100 mV, it must be modified. The addition of an appropriate level control is described fully in the RX meter instruction manual. In this discussion,  $R_T$  refers to the total load resistance seen by the collector.  $R_L$ , the external load, is included in  $R_T$ .

Figure 3-4. Single-tuned amplifier connection.

except the crystal loss. The crystal loss is included in the following manner.

Step 1. The ratio of the total feedback power to the transistor input power is given by

$$\frac{P_{\rm FB}}{P_{\rm in}} \doteq \frac{(R_{\rm in} + R_e)}{R_{\rm in}},\tag{3-3}$$

Figure 3-5. Input resistance and power gain versus load for 2N2218 transistor. 28, 29

where

$P_{\rm FB}$  = total feedback power,

$P_{\rm in}$  = the power input to the active device,

$R_{\rm in}$  = the input resistance of the transistor, and

$R_e$  = the series resonant resistance of the crystal.

Incorporating this loss due to the crystal into the input circuit gives the modified power gain  $G'_p$  as

$$G_p' = \frac{G_p R_{\rm in}}{(R_{\rm in} + R_s)}.$$

(3-4)

Step 2. The next step is to determine the ratio of the output power to the feedback power. All losses are accounted for now; therefore,

$$P_o = P_L + P_{\rm FB}. \tag{3-5}$$

The output power also is given by

$$P_o = (P_{\rm FB} G_p').$$

(3-6)

Combining equations (3-5) and (3-6) gives

$$(P_{\rm FB} G_p') = P_L + P_{\rm FB},$$

(3-7)

or

$$P_{\rm FB} = \frac{P_L}{(G'_n - 1)}. (3-8)$$

$P_{\rm FB}$  can be represented by an equivalent resistor  $R_{\rm FB}$  (whose power dissipation is  $P_{\rm FB}$  placed in parallel with the external load  $R_L$ .  $R_L$  and  $R_{\rm FB}$  are subjected to the same voltage; therefore, the resistance ratio is inverse to the power ratio, and

$$R_{\rm FB} = R_L (G_p' - 1). \tag{3-9}$$

Now  $R_T$ , the total load resistance, is the parallel combination of  $R_{\rm FB}$  and  $R_L$ ; using this with equation (3-9) and rearranging terms gives

$$R_L = \frac{R_T G_p'}{(G_p' - 1)} \tag{3-10}$$

and

$$R_{\rm FB} = R_T G_p'. \tag{3-11}$$

Using equations (3-10) and (3-11), the values of  $R_{\rm FB}$  and  $R_L$  can be determined. The use of a  $G_p'$  of one-third to one-half the value determined from equation (3-4) should provide an adequate feedback power safety factor.

Step 3. The last step in the procedure is the determination of the required impedance transformation ratio of the feedback circuit. This is the ratio of  $R_{\rm FB}$  to  $(R_{\rm in} + R_e)$  or

Required impedance transformation ratio =

$$\frac{R_{FB}}{(R_{in} + R_e)}$$

. (3-12)

There are several types of impedance transforming networks which can be used, e.g., a capacitive tap on the output tuned circuit, a pi network, or a transformer. The properties of specific networks are treated briefly with the discussion of particular oscillator circuits in Chapter 7. Detailed discussions of several feedback networks are given in references 31, 32, and 35.

The power gain approach to the design of crystal oscillators is one of the few approaches simple enough to be of practical value. Accuracy is only fair and the difference from actual oscillator loop gain normally will not exceed 2 or 3. Also, a considerable amount of component value adjusting usually is necessary to get the crystal to operate on frequency. The approach is of the most value in designing oscillators of high frequency and high output power.

In general, the Y-parameter approach is a better design method for low-power oscillators. (If, however, the Y-parameters of a transistor are not known, or if from other considerations the reader elects to use the power gain method, it is suggested that reference 31 be consulted, since only the principles of this approach have been outlined here, and a detailed explanation of each step is given in the reference.)

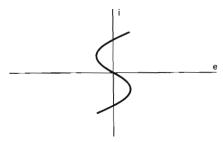

## 3.4. NONLINEAR MODIFICATIONS

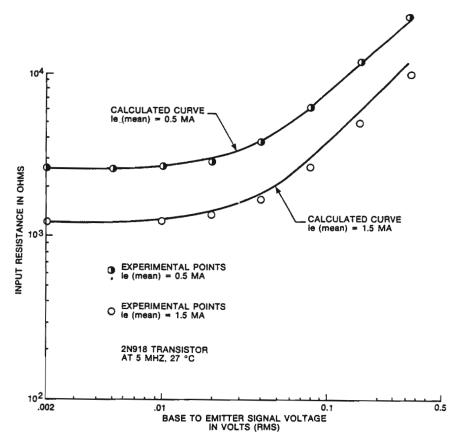

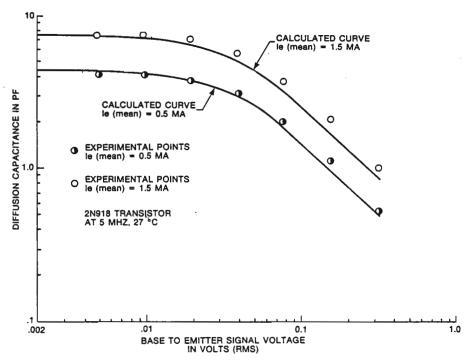

The small-signal analysis discussed in section 3.2 is valid until the ac base-to-emitter voltage builds up to about 10 mV. For values greater

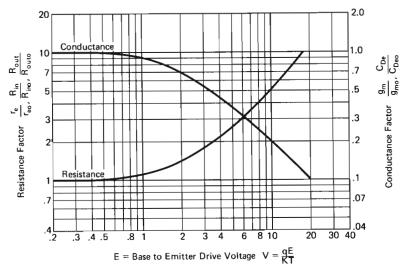

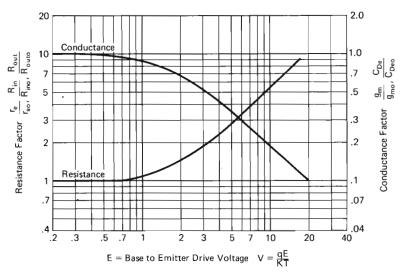

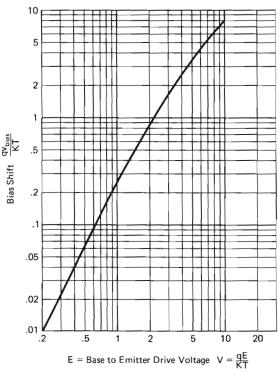

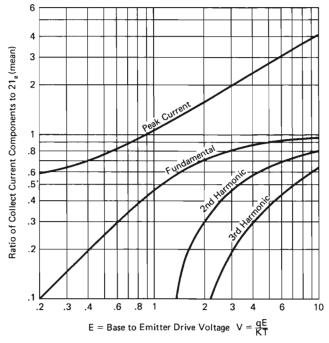

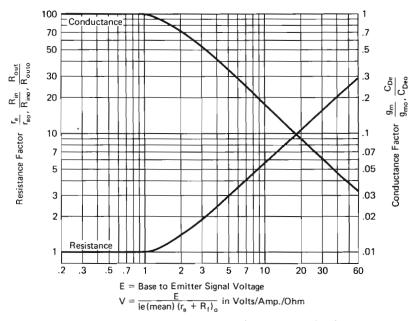

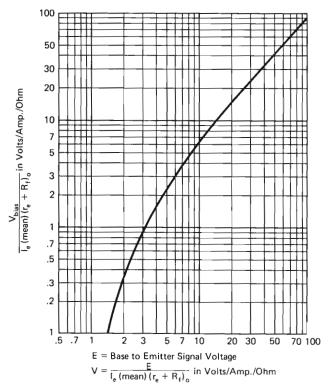

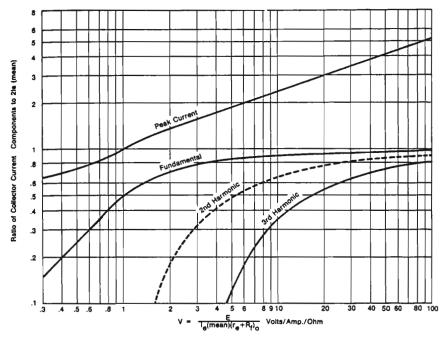

than this, significant changes occur in the forward transconductance as well as the input and output impedances. The magnitude of these changes is derived in Appendix G for the basic transistor and in Appendix H for a transistor with emitter degeneration. If the initial loop gain determined by  $g_f$  (transistor)/ $g_f$  (required) is calculated, the result can then be used to predict the base-to-emitter voltage, the input and output impedances, the harmonic current, and the bias shift. The curves of Figure 3-6 illustrate the method.

Suppose that the initial loop gain is 3. After the amplitude of oscillation has built up to its equilibrium value, the actual loop gain will be unity. Therefore the ratio  $g_m/g_{m0}$  must be 0.333. From Figure 3-6 we see that V, the normalized ac base-to-emitter voltage, will be 5.7. The actual base voltage is then 5.7 KT/q where

$K = \text{Boltzman's constant}, 1.38 \times 10^{-23} \text{ J/}^{\circ}\text{K};$

q = electron charge, 1.602  $\times$  10<sup>-19</sup> C; and

$T = \text{temperature in }^{\circ} K$ .

At room temperature KT/q = 26 mV; therefore, the actual voltage is  $5.7 \times 26 = 148.2$  mV.

Once the base voltage is known, it is normally fairly straightforward to calculate the voltage in any other part of the circuit.

Figure 3-6. Transistor parameters versus signal voltage.

It should be noted that the input capacitance is reduced by the same ratio as the small-signal loop gain, which results in a slight increase in frequency.

Curves showing the harmonic currents as well as the bias shift are presented in Chapter 6. They may be useful in predicting the performance of the oscillator if a harmonic of the fundamental frequency is used.

Specific nonlinear equations, based on the principle of harmonic balance, are also derived for the Colpitts oscillator in Appendix I, and the results are presented in section 7.3.

# 4

# Oscillator Frequency Stability

The term frequency stability is a generic term which means a variety of things to different people depending on their individual interests. In its broadest concept, it means the degree of constancy of the frequency of an oscillator under a particular set of conditions. In crystal oscillator applications, there are several different types of frequency stability:

- a. Frequency stability as affected by environmental changes consisting primarily of temperature, voltage, and load variations.

- b. Long-term frequency drift as affected by aging of the quartz crystal resonator.

- c. Short-term frequency stability or phase stability.

Frequency stability is used in this book to mean either a or b, both of which will be discussed in this chapter. In some specifications frequency stability is meant to be the sum of a and b; however, because so much misunderstanding has resulted, it is recommended that when this usage is adopted it should be clearly stated that frequency stability is meant to include both environmental stability and aging for a specified time period. The term frequency accuracy is also sometimes specified and is a measure of the actual frequency compared to an established standard. It results from the initial setting error and the stability.

## 4.1. TEMPERATURE EFFECTS ON FREQUENCY

The frequency of a crystal oscillator is affected by changes in ambient temperature. These changes in temperature can affect the value of any of the components which comprise the oscillator circuit. If these component variations do not cancel each other, a change in the nominal operating frequency of the oscillator will result. The frequency determining component most severely affected by any temperature change is the quartz crystal. This effect is shown graphically for AT-cut crystals in Chapter 5, Figure 5-6. (A discussion of the temperature coefficients of other crystal cuts can be found in reference 6.)

In some applications, sufficient frequency stability can be obtained from the quartz crystal. The limit obtainable over the full military temperature range of -55°C to +105°C with an AT-cut crystal is approximately ±0.002 percent. This limit can be improved within a reduced temperature range. Many applications require stabilities considerably better. In such cases, two methods are available for eliminating or reducing the effects of temperature changes on the crystal oscillator, namely, temperature control and temperature compensation.

# 4.1.1. Temperature Control

The degree of temperature control required on a particular oscillator is determined primarily by the specifications of the system in which it is to be used. Stabilities of approximately ±5 parts in 10<sup>7</sup> can be obtained using plug-in crystal ovens with the oscillator circuitry external to the oven. Stabilities to several parts in 10<sup>9</sup> can be obtained with proportionally controlled ovens containing the crystal and oscillator circuitry. (A proportionally controlled oven uses a temperature-controlling system in which the power supplied to the oven is proportional to the heat loss. (Refer to section 9.3.) For stabilities better than 5 parts in 10<sup>9</sup>, it is generally necessary to use a two-stage oven. This may be a combination of two ovens with a single control circuit or two independent proportionally controlled ovens.

Crystal ovens have several disadvantages which tend to limit their usage in some applications. These are as follows:

- 1. A warm-up time is required.

- 2. The volume is relatively large.

- 3. The power consumption is high.

- 4. The reliability of the components in the oven is reduced if the application requires frequent turning on and off of the oven.

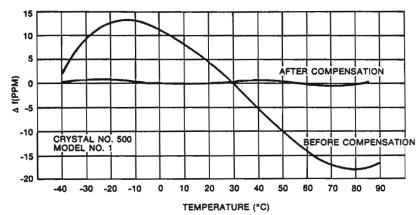

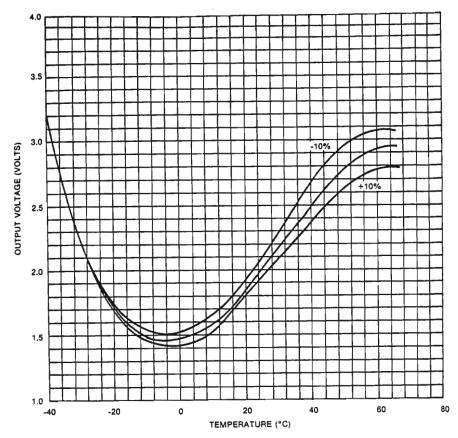

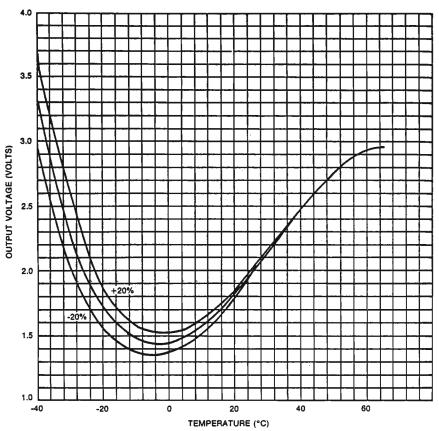

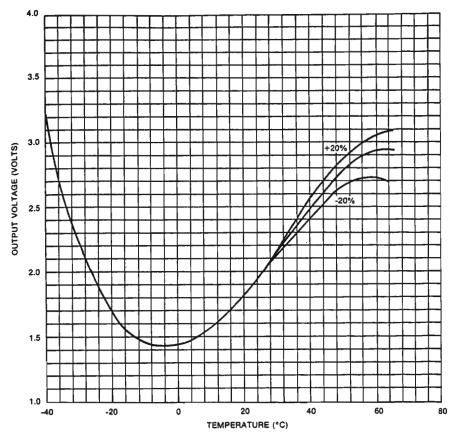

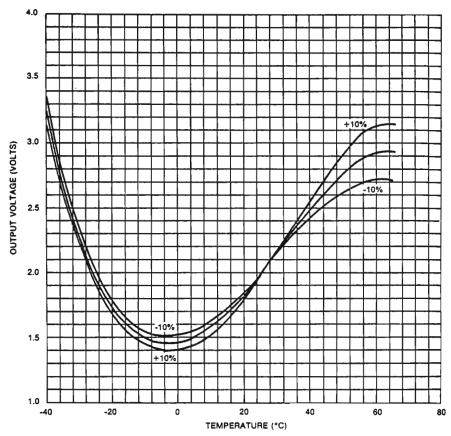

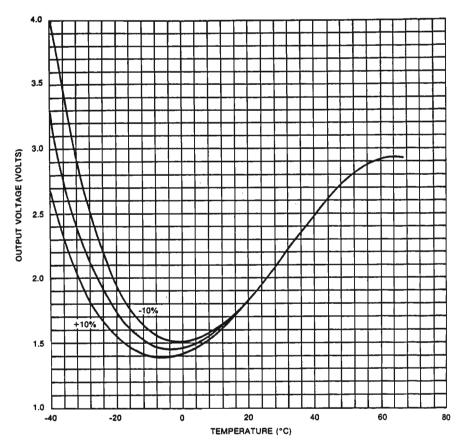

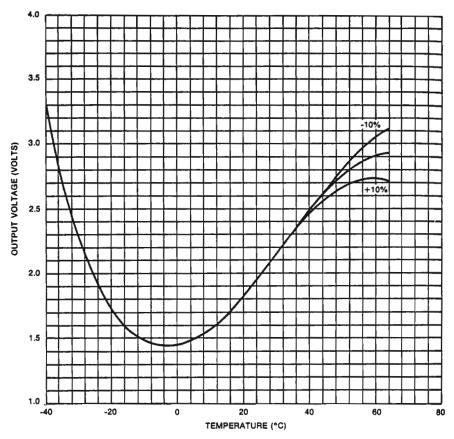

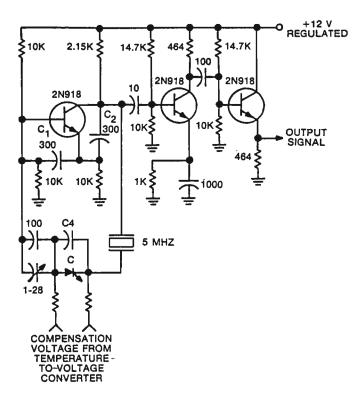

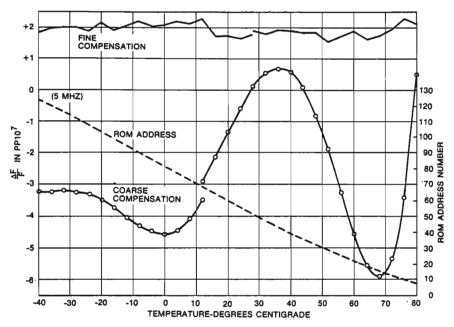

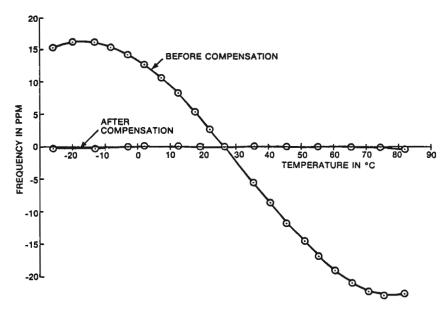

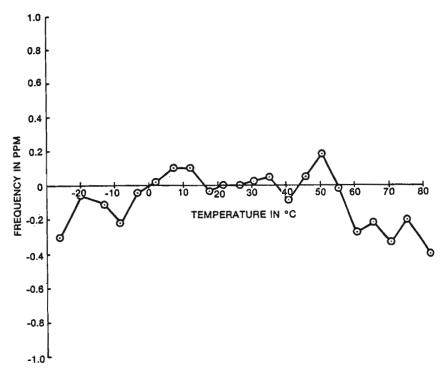

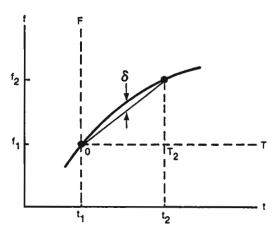

Figure 4-1. Frequency versus temperature characteristic for a typical temperature-compensated crystal oscillator.

## 4.1.2. Temperature Compensation

Temperature compensation of crystal oscillators is very practical to achieve frequency stabilities in the range of  $\pm 10$  to  $\pm 0.5$  ppm. With considerable care, compensation to  $\pm 0.05$  ppm is possible.

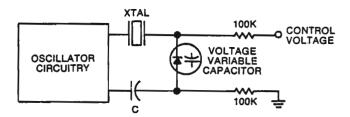

Temperature compensation is generally achieved by placing a voltage variable capacitor in series with the crystal. A voltage is then applied to the capacitor, which pulls the crystal frequency by precisely the amount that it drifted in temperature but in the opposite direction. The voltage is generated either by a thermistor-resistor analog network or by a digital system followed by a digital-to-analog converter.

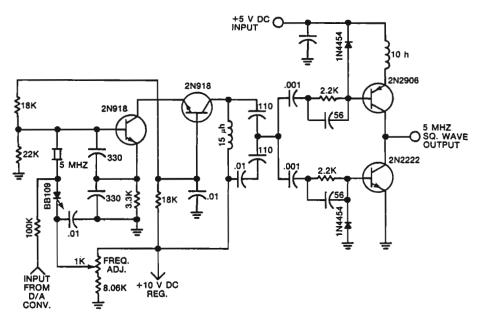

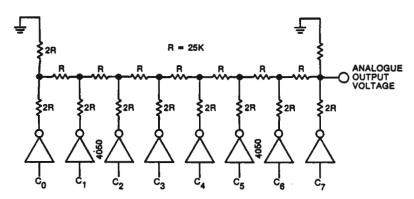

The means for temperature compensation are discussed in considerable detail in Chapter 10. Figure 4-1 shows the improvement in frequency that was achieved using a three-thermistor analog network in a 3.2-MHz crystal oscillator.

## 4.2. LONG-TERM FREQUENCY DRIFT

The phrase *long-term frequency drift* usually refers to the gradual drift in average frequency of an oscillator due to aging of components, notably the quartz crystal. It is not meant to include the short-term variations discussed in section 4.3 or the deviations due to ambient

temperature change discussed in section 4.1. The aging of a quartz crystal itself is discussed in section 5.7.

# 4.3. SHORT-TERM FREQUENCY STABILITY

The phrase short-term frequency stability refers to changes in the oscillator frequency which result from interaction of the desired signal with an unwanted signal or noise. It is not meant to include frequency variations due to component aging or ambient temperature change. The type of interaction may be simple superposition, amplitude modulation, frequency modulation, phase modulation, or any combination thereof. Only in the case of FM or PM is there a true change in frequency. The other types may cause an apparent change in frequency which may vary with different frequencymeasuring techniques. For this reason, the signal-to-noise ratio or sideband level of an oscillator is sometimes specified. If phase modulation is the only type of interaction being considered, or is predominant, the term phase stability may be used in place of short-term frequency stability. Frequency modulation and phase modulation are related by the modulation frequency. If the undesirable signal is sinusoidal, this relationship is given by

$$\Delta\theta = \frac{\Delta f}{f_m}$$

where  $\Delta\theta$  is the peak phase deviation in radians,  $\Delta f$  is the peak carrier frequency deviation, and  $f_m$  is the frequency of the undesirable signal.

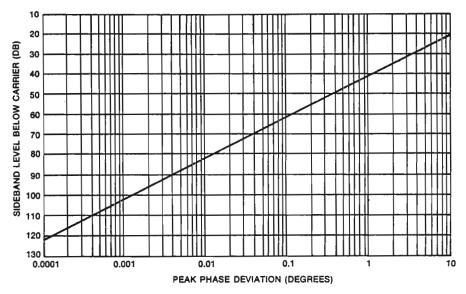

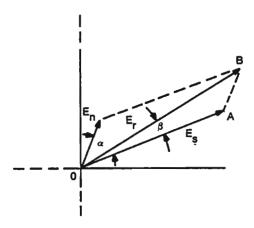

As is the case of any FM or PM signal, theoretically an infinite number of sidebands exist. The total phase deviation is usually so small with crystal oscillators, however, that only the first pair of sidebands is significant. The relationship between these sidebands and the phase deviation is given in Figure 4-2. This graph does not consider the presence of AM. The mathematical development of Figure 4-2 is given in Appendix J. In the case of noise modulation, the sideband levels are often specified in decibels below the carrier per hertz of bandwidth (dB/Hz). For a narrow-bandwidth measurement system, pure FM or PM noise modulation results in the same sideband level as shown in Figure 4-2. Here the sideband level is in-

Figure 4-2. Sideband level versus phase deviation.

terpreted to be the ratio of the rms value of the noise sideband to the rms value of the carrier, and the abscissa is  $\sqrt{2}$  times the rms phase deviation. For noise simply added to the signal, the sidebands are uncorrelated and the apparent phase deviation is 3 dB lower for the same sideband level. The rms phase jitter is then given by  $\Delta\theta = 10^{-dB/20}$  rad rms, where dB refers to the level of either the upper or lower sideband in a bandwidth numerically equal to the baseband in which the phase jitter is measured.\*

In many cases short-term frequency stability is best specified in the time domain and is given as the rms fractional frequency deviation for some specified measurement time  $\tau$ . For example a precision crystal oscillator might exhibit a short-term stability of  $1 \times 10^{-11}$  rms for one-second averaging times. If a large number of frequency measurements, say n, are made using an averaging time of  $\tau$  seconds, the standard deviation can be computed using the statistical relationship

<sup>\*</sup>Short-term frequency stability and/or phase noise can be conveniently measured using a phase-locked loop with two identical oscillators, with a spectrum analyzer, a computing frequency counter, or a frequency stability analyzer.

$$\sigma_n^2(\Delta f) = \frac{1}{n-1} \left[ \sum_{i=1}^n (f_i)^2 - \frac{1}{n} \left( \sum_{i=1}^n f_i \right)^2 \right]. \tag{4-1}$$

It has been found, however, that for large numbers of measurements, the elapse time is so large that frequency aging and temperature effects tend to influence the results and  $\sigma$  becomes a function of how long the test was run. A better method and one which has become standard is to use the Allan variance. In using this method individual variances are computed from adjacent pairs of frequency readings and the average of the variances forms the basis for the definition.

Taking n = 2, equation (4-1) simplifies to

$$\sigma_2^2(\Delta f) = \frac{(f_1 - f_2)^2}{2}. (4-2)$$

The frequency stability is then found by taking the square root of the average of the variances, and is

$$\sigma_{y}(\tau) = \left[\frac{1}{2N} \sum_{i=1}^{N} (f_{2i} - f_{2i-1})^{2}\right]^{1/2}$$

(4-3)

where  $\tau$  is the measurement time for each frequency reading with no dead time between readings, and N is the number of measurement pairs used. A fairly large number of readings is required to compute a reliable value of  $\sigma_{\nu}(\tau)$ , and N=100 is quite common.

The time domain method of specifying short-term frequency stability is useful for counting intervals ranging from less than a millisecond to about 100 seconds. It is possible to convert from time domain measurements to frequency domain performance and vice versa. Indeed this is a very powerful method of determining the frequency spectral content of an oscillator within a fraction of 1 Hz of the carrier.<sup>51</sup> In general, however, it is best to specify the characteristic which is actually important to the system. For example if it is the phase stability that is important than this should be specified.

The art of designing oscillators for best short-term frequency stability is not treated in this book; however, it should be pointed out that it is a very important consideration in the design of some oscillators. A rigorous definition of short-term frequency stability is itself quite complex, and the reader is referred to reference 52 for a comprehensive treatment of the subject.

# 5

# Quartz Crystal Resonators

The importance of quartz crystal resonators in electronics results from their extremely high Q, relatively small size, and excellent temperature stability.

A quartz crystal resonator utilizes the piezoelectric properties of quartz. If a stress is applied to a crystal in a certain direction, electric charges appear in a perpendicular direction. Conversely, if an electric field is applied, it will cause mechanical deflection of the crystal. In a quartz crystal resonator, a thin slab of quartz is placed between two electrodes. An alternating voltage applied to these electrodes causes the quartz to vibrate. If the frequency of this voltage is very near the mechanical resonance of the quartz slab, the amplitude of the vibration will become very large. The strain of these vibrations causes the quartz to produce a sinusoidal electric field which controls the effective impedance between the two electrodes. This impedance is strongly dependent on the excitation frequency and possesses an extremely high  $\mathcal{Q}$ .

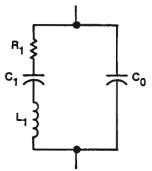

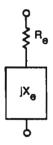

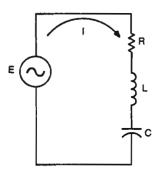

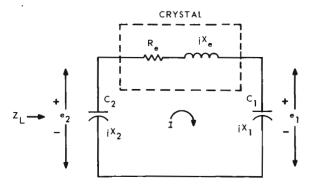

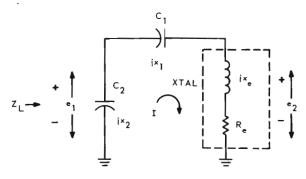

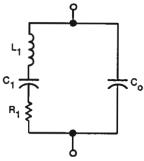

Electrically, a quartz crystal can be represented by the equivalent circuit of Figures 5-1 and 5-2 where the series combination  $R_1, L_1$ , and  $C_1$  represent the quartz, and  $C_0$  represents the shunt capacitance of the electrodes in parallel with the holder capacitance. The inductor  $L_1$  is a function of the mass of the quartz, while  $C_1$  is associated with its stiffness. The resistor  $R_1$  results from the loss in the quartz and in the mounting arrangement. The parameters of the equivalent circuit can be measured quite accurately using the crystal impedance (CI) meters,\* vector voltmeters,  $^{14,49}$  or bridge measurement tech-

<sup>\*</sup>RFL Industries, Boonton, NJ, Model 5950, with plug-in units to cover frequency of interest. Old crystal impedance meters are TS-710/TSM, 10-1100 kHz, TS-630/TSM, 1-15 MHz; TS-683/TSM, 10-140 MHz; and AN/TSM-15, 75-200 MHz.

Figure 5-1. Simplified diagram of the equivalent circuit of a quartz crystal

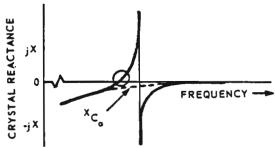

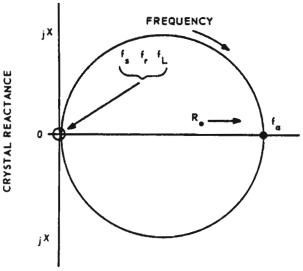

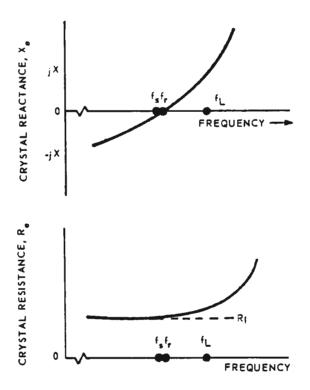

niques.<sup>19</sup> A reactance-frequency plot of the equivalent circuit is given in Figure 5-3, and a reactance-resistance plot is given in Figure 5-4. The portions circled on these figures are expanded in Figure 5-5.

Several equations have been derived in Appendix K which are useful when using the equivalent circuit. The results are presented below. Several frequencies are marked in Figures 5-4 and 5-5. The first of these is  $f_s$ . This is the frequency at which the crystal is series resonant, and is given by

$$f_s = \frac{1}{2\pi\sqrt{L_1C_1}}$$

(5-1)

where

$f_s$  = series resonant frequency in hertz,

$L_1$  = motional arm inductance in henrys, and

$C_1$  = motional arm capacitance in farads.

Figure 5-2. Impedance representation of a quartz crystal.

Figure 5-3. Plot of reactance versus frequency for a quartz crystal.

The second point,  $f_r$ , represents the frequency at which the crystal appears purely resistive  $(X_e=0)$ . Point  $f_r$  is different from  $f_s$  only because of the presence of  $C_0$ , and for practical purposes can be considered equal to  $f_s$ . The third point labeled,  $f_L$ , is the frequency at which the crystal is antiresonant with a given external capacitor  $C_L$ . If  $\Delta f$  is the frequency shift  $(f_L - f_s)$  between series resonance and this load point, then

Figure 5-4. Plot of reactance versus resistance for a quartz crystal.

Figure 5-5. Expanded portions of crystal reactance (A) and resistance, (B). (See Figures 5-3 and 5-4).

where

$\Delta f = \text{frequency shift}$

$$(f_L - f_s)$$

in hertz,

$C_1$  = motional arm capacitance in picofarads,

$C_0$  = crystal holder capacitance in picofarads, and

$C_L$  = external load capacitance in picofarads.

The point labeled  $f_a$  is the antiresonant frequency of the crystal with its own holder capacitance  $C_0$ . It is given by

$$f_a = f_s \left[ 1 + \frac{C_1}{2C_0} \right]$$

(5-3)

where

$f_a$  = antiresonant frequency in hertz,

$f_s$  = series resonant frequency in hertz,

$C_1$  = motional arm capacitance in picofarads, and

$C_0$  = crystal holder capacitance in picofarads.

Furthermore, it can be shown (see Appendix K) that the equivalent resistance  $R_e$  in the region between series  $(f_s)$  and antiresonance  $(f_a)$  is given by

$$R_e = R_1 \left( \frac{C_L + C_0}{C_L} \right)^2$$

(5-4) provided the assumption  $\left| X_{C_0} \left( \frac{C_L}{C_0 + C_L} \right) \right| >> R_1$  is true, where

$$X_{C_0} = -\frac{1}{2\pi f C_0}.$$

Normally a crystal is operated between its series resonant frequency and its antiresonant frequency so that the reactance  $X_e$  is either zero or inductive.

To help the engineer acquire a practical grasp of the equivalent circuit, Table 5-1 is included to give a rough idea of the magnitude of the various equivalent circuit components.

The parameters of a quartz crystal resonator may be varied greatly by the angle at which the crystal blank is cut from the raw quartz and by the mode of vibration. This is primarily a concern of the crystal manufacturer and will not be discussed in detail here. (An excellent

| Parameters | 200-kHz <sup>31</sup><br>fundamental | 2-MHz <sup>31</sup><br>fundamental | 30-MHz <sup>31</sup><br>third overtone | 90-MHz<br>fifth overtone |

|------------|--------------------------------------|------------------------------------|----------------------------------------|--------------------------|

| $R_1$      | 2 kΩ                                 | 100 Ω                              | 20 Ω                                   | 40 Ω                     |

| $L_1$      | 27 H                                 | 520 mH                             | 11 mH                                  | 6 mH                     |

| $C_1$      | 0.024 pF                             | 0.012 pF                           | 0.0026 pF                              | 0.0005 pF                |

| $C_0$      | 9 pF                                 | 4 pF                               | 6 pF                                   | 4 pF                     |

| Q          | $18 \times 10^{3}$                   | $54 \times 10^{3}$                 | 10 <sup>5</sup>                        | $85 \times 10^{3}$       |

Table 5-1. Typical Crystal Parameter Values.

treatment of crystal cuts is given in reference 6.) Several properties of crystal resonators are of concern to the designer of crystal oscillators and will be discussed in the following paragraphs.

# 5.1 LOAD CAPACITANCE

From Figures 5-3, 5-4, and 5-5 it can be seen that the frequency of the crystal will vary to some extent depending upon the reactance that the crystal must present to an external circuit. Since the frequency difference between series and antiresonance  $(f_a - f_s)$  may be on the order of 1 percent for some crystals, it is important that the crystal be ground to frequency at the load reactance value with which it will be used in the oscillator. Four load conditions have become standard and are nearly always used. With the first two of these, the crystal acts like an inductive reactance which will resonate with either 30 or 32 pF at the operating frequency. Hence, the load capacitance  $C_L = 30 \,\mathrm{pF}$  or  $C_L = 32 \,\mathrm{pF}$ . Crystals of this type must be used in parallel resonant oscillators. A second common load point is series resonance, where the crystal acts like the resistor  $R_1$ . Crystals of this type must be used with series resonant oscillators. A fourth load point,  $C_L = 20 \,\mathrm{pF}$ , is sometimes used for crystals below 500 kHz.

### 5.2 PIN-TO-PIN CAPACITANCE

Pin-to-pin capacitance ( $C_0$  of Figure 5-1) refers to the capacity of the electrodes on the quartz as well as that of the holder itself. The holder capacitance is usually around 0.5 pF and the remaining capacitance is due to the electrodes plated on the quartz.  $C_0$  should be restricted to about 5 pF for AT-cut\* crystals while it may be somewhat higher for low-frequency cuts. It becomes important to minimize  $C_0$  for VHF crystals, where it may cause the oscillator to free-run (to oscillate not crystal-controlled).  $C_0$  may be reduced in crystal manufacture by reducing the electrode spot size on the crystal blank. However, this tends to increase the resistance  $R_1$ .

<sup>\*</sup>The AT-cut is the basic high-frequency crystal normally used in the range from 1 to 150 MHz.

### **5.3 RESISTANCE**

The resistance of a crystal is specified at the rated load capacitance, although this usually does not differ grossly from the series resistance  $R_1$ . The maximum allowable resistance for a given crystal type may vary from about 40  $\Omega$  for VHF crystals to approximately 500 k $\Omega$  for audio-frequency crystals. It is important to make certain that an oscillator will function properly with a crystal of the maximum specified resistance.

### 5.4 RATED OR TEST DRIVE LEVEL

Drive level refers to the power dissipated in the crystal. Rated or test drive level is the power at which all requirements of the crystal specification must be met. The drive level specification should reasonably duplicate the actual drive level at which the crystal will be used because frequency is somewhat dependent on drive level. AT-cut crystals generally can withstand a considerable overdrive without physical damage; however, the electrical parameters are degraded at excessive drive. Low-frequency crystals (especially flectural mode crystals) may fracture if overdriven. Drive level ratings vary from 5  $\mu$ W below 100 kHz to about 10 mW in the 1- to 20-MHz region for fundamental mode crystals. Overtone crystals which are generally used above 20 or 30 MHz are often rated at 1-2 mW of drive.

### 5.5 FREQUENCY STABILITY

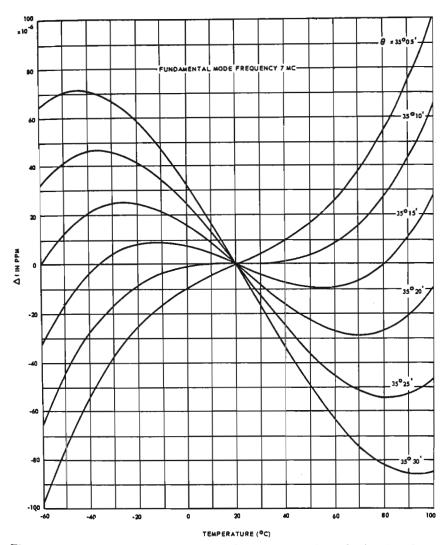

The frequency stability of a crystal generally is limited by its temperature coefficient and aging rate. AT-cut crystals have a better temperature coefficient than most other cuts. Common frequency tolerance specifications are  $\pm 0.005$  percent or  $\pm 0.0025$  percent from  $-55^{\circ}$ C to  $+105^{\circ}$ C. These include calibration tolerance; thus, the actual temperature coefficient is slightly better. Improved temperature coefficients can be obtained if the temperature range is limited. This can be seen in Figure 5-6, which gives frequency-temperature curves for AT-cut crystals. These curves may be represented by cubic equations and are strongly dependent on the angle of cut of the quartz blank from the mother crystal. The points of zero temperature coefficient

Figure 5-6. Frequency-temperature-angle characteristics of plated AT-type natural quartz crystal resonators.<sup>4</sup>

are called the turning points (lower and upper turning-point temperatures). One turning point can be placed where desired by selecting the angle of cut; the other turning point then is determined, since the turning points are symmetrical about a point in the 20-30°C range.

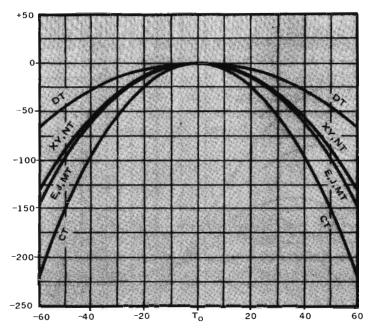

Figure 5-7. Frequency-temperature characteristics of low-frequency crystal cuts. (Courtesy Northern Engineering Laboratories)

The slope between the turning points becomes smaller as the turning points move together. Crystals designed for use in an oven should be cut so that a turning point occurs at the oven temperature. Figure 5-7 shows the frequency-temperature curves for several low-frequency cuts. The J-cut is used below 10 kHz, while an XY-cut may be used from about 3 kHz to 85 kHz. An NT-cut may be used in the 10 kHz to 100 kHz range. A DT-cut is applicable from 100 kHz to about 800 kHz and a CT from perhaps 300 kHz to 900 kHz.

#### 5.6. FINISHING OR CALIBRATION TOLERANCE

Finishing tolerance is the maximum allowable error in frequency of a crystal at some specified temperature. If  $\pm 0.005$ -percent crystals are used, it is often desirable to specify a room temperature finishing tolerance of, e.g.,  $\pm 0.0015$  percent so that oscillators can be tuned conveniently to frequency in production. If oscillators are to be tuned

to frequency, the finishing tolerance must be less than the tuning range of the oscillator. In the case of temperature controlled crystals, the finishing tolerance is specified at the nominal operating temperature of the oven. Another use of finishing tolerance is with an alternative method of specifying the overall frequency tolerance of a crystal. It is sometimes desirable to specify a room temperature finishing tolerance and a maximum deviation from the room temperature frequency over the temperature range. This method may be used in place of specifying a frequency tolerance as described in section 5.5.

### 5.7. CRYSTAL AGING

Crystal aging is caused primarily by a gradual transfer of mass to or from the crystal blank and by a relaxation of stresses. Generally it is slowed down by operating the crystal at low drive level and at low temperature; however, it is most important that the crystal be kept clean. For this reason, it is essential that the hermetic seal of the crystal be preserved. Aging of cold-weld and glass enclosed crystals is significantly slower than that of crystals in solder sealed cans, since they can be kept cleaner. Glass enclosed crystals usually age up in frequency due to an apparent reduction in the mass of the quartz blank, while metal enclosed crystals age down in frequency because impurities settle on the blank.

Aging rate specifications are generally  $\pm 0.0005$  percent per month for standard military-type (MIL-type) crystals; however, it is possible to achieve aging rates as low as 1 part in  $10^{11}$  per day for precision crystals. Ordinary crystals enclosed in cold-weld holders can be expected to age 1-5 parts in  $10^8$  per week after the first year. Aging is not accounted for in the overall temperature specification as discussed previously.

### 5.8. Q AND STIFFNESS OF CRYSTALS

The Q of ordinary or MIL-type crystals is normally not specified, but for standard units, it usually falls between 20,000 and 200,000. Precision crystals may have Q values as high as  $5 \times 10^6$ . Q is defined as  $X_L/R_1$ , where  $X_L$  is the reactance of  $L_1$  at the operating frequency.

The  $C_0/C_1$  ratio of a crystal usually is not specified. It is a measure

of the stiffness of the crystal, as can be seen from equation (5-3). When the pulling characteristics of a crystal are important, it should be specified. Typical  $C_0/C_1$  ratios may be on the order of 1000, although it is possible to achieve  $C_0/C_1$  ratios from 125 to over 35,000.

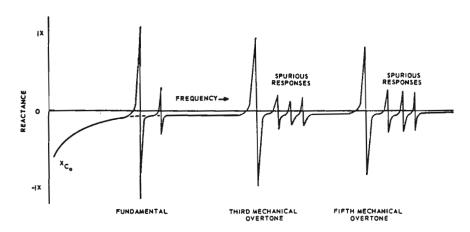

### 5.9. MECHANICAL OVERTONE CRYSTALS

The AT-cut crystals may be operated on their fundamental frequency or on odd mechanical overtones, notably the third and the fifth overtones. Overtone crystals normally are used above 20 MHz. They have higher Q values, better aging rates, and are electrically stiffer than fundamental crystals of the same frequency. A tuned circuit is necessary in the oscillator to ensure operation on the proper overtone. Overtone crystals are nearly always operated at series resonance. The overtone responses of a crystal should not be confused with harmonics of the fundamental frequency. They are two different phenomena. The overtone responses of a crystal are in general not exactly multiples of the fundamental frequency, although they are close. These overtone responses are depicted in Figure 5-8 which shows, in general, the various responses which may be expected in a typical AT-cut crystal. The spurious responses are discussed in section 5.10.

Figure 5-8. Overtone response of a quartz crystal.

As a general rule, third-overtone crystals are used from 20 to 60 MHz and fifth overtones from 60 to 125 MHz.\*

### 5.10. SPURIOUS OR UNWANTED MODES

There are always a number of spurious responses in a quartz crystal in addition to the response of interest. This results from the fact that various modes of vibration are possible in any given quartz blank. Although the number, magnitude, and frequencies of the unwanted modes vary from crystal to crystal, an arbitrary arrangement is shown in Figure 5-8. Most of the spurious responses have a high resistance compared to the main response; however, a few low-resistance responses usually exist. They are almost always higher in frequency than the main response, and for AT-cut crystals very often fall within 200 kHz of the main response. If a spurious response has a resistance which is too low with respect to the main response, the oscillator circuit may operate on the frequency of the spurious rather than on the main response.

Generally, no problem with spurious responses is encountered using fundamental-mode crystals. With overtone crystals, however, problems frequently are encountered. It is desirable to specify a large spurious-to-main-response resistance ratio to avoid the possibility of trouble. Practically, however, it is difficult to eliminate the unwanted responses, although several techniques are available to reduce them. With third overtone crystals, a 2-to-1 spurious ratio specification is fairly common, although often inadequate, while a 4-to-1 ratio is practical even in large production quantities. With fifth-overtone crystals, it is somewhat more difficult to make the spurious resistance high, but a 3-to-1 minimum ratio is still practical. It is often desirable to specify not only a minimum ratio but also a minimum permissible spurious resistance. This results from the fact that a larger spurious ratio is required when the crystal resistance is low. For a discussion of the spurious effects in oscillator circuits, the reader is referred to section 9.5.

<sup>\*</sup>A considerable amount of research is being conducted in the area of surface acoustic wave resonators. These devices, which may be represented by the same equivalent circuit as the bulk wave resonators discussed in this section, show promise of extending the frequency range of crystal oscillators into the low gigahertz region. The  $C_0/C_1$  ratio of these devices is roughly equivalent to a fifth overtone AT-cut; however, the TC is parabolic in shape.

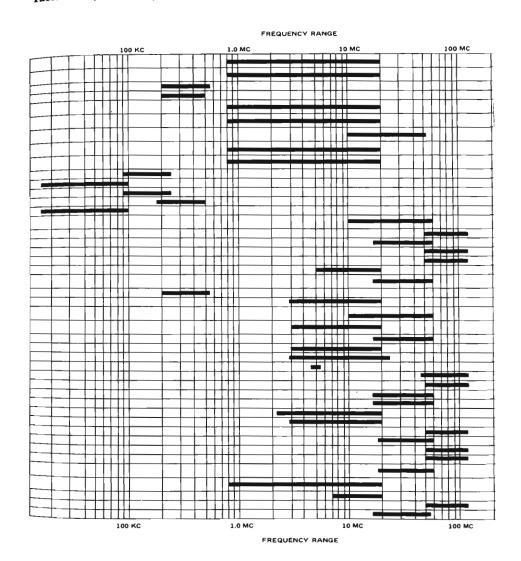

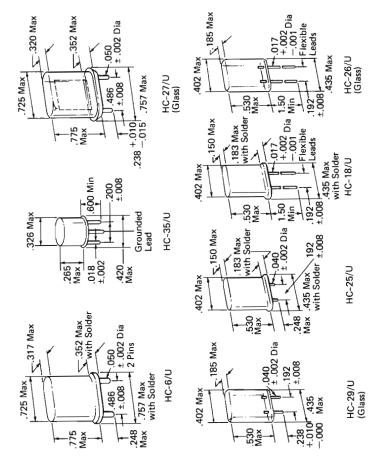

Table 5-2. Summary of Selected MIL Crystals (compiled from MIL-STD-683D).

|                 |         |                                        |                                 |        |       |                           | _ |

|-----------------|---------|----------------------------------------|---------------------------------|--------|-------|---------------------------|---|

| CRYSTAL<br>TYPE | HOLDER* | OVER-ALL<br>FREQUENCY<br>TOLERANCE (%) | OPERATING<br>TEMP RANGE<br>(°C) | LOAD   | MODE  | RATED DRIVE<br>LEVEL (MW) |   |

| CR-18A/U        | HC-6/U  | ±.005                                  | -55 TO +105                     | 32 PF  | FUND  | 19 {≶18 MS}               |   |

| CR-19A/U        | HC-6/U  | ±.005                                  | -55 TO +105                     | SERIES | FUND  | 19 {≶}8 MS}               | Г |

| CR-25B/U        | HC-6/U  | ±.01                                   | -40 TO +85                      | SERIES | FUND  | 2.0                       | Г |

| CR-26A/U        | HC-6/U  | ±.002                                  | +70 TO +80                      | SERIES | FUND  | 2.0                       | Г |

| CR-27A/U        | HC-6/U  | 1.002                                  | +70 TO +80                      | 32 PF  | FUND  | 5.5 {≶18 MS}              |   |

| CR-28A/U        | HC-6/U  | ±.002                                  | +70 TO +80                      | SERIES | FUND  | 5.5 {≶18 MS}              | Г |

| CR-32A/U        | HC-6/U  | 1.002                                  | +70 TO +80                      | SERIES | THIRD | ₹ (≶25 MS)                |   |

| CR-35A/U        | HC-6/U  | ±.002                                  | +80 TO +90                      | SERIES | FUND  | 5.5 (≶18 MS)              |   |

| CR-36A/U        | HC-6/U  | ±.002                                  | +80 TO +90                      | 32 PF  | FUND  | 5.5 {≶18 MS}              |   |

| CR-37A/U        | HC-13/U | ±.02                                   | -40 TO +70                      | 20 PF  | FUND  | 2.0                       |   |

| CR-38A/U        | HC-13/U | ±.012                                  | -40 TO +70                      | 20 PF  | FUND  | 0.1                       |   |

| CR-42A/U        | HC-13/U | ±.003                                  | +70 TO +80                      | 32 PF  | FUND  | 2.0                       |   |

| CR-47A/U        | HC-6/U  | ±.002                                  | +70 TO +80                      | 20 PF  | FUND  | 2.0                       |   |

| CR-50A/U        | HC-13/U | ±.012                                  | -40 TO +70                      | SERIES | FUND  | 0.1                       | Г |

| CR-52A/U        | HC-6/U  | ±.005                                  | -55 TO +105                     | SERIES | THIRD | 4:8 {≶25 MS}              |   |

| CR-54A/U        | HC-6/U  | ±.005                                  | -55 TO +105                     | SERIES | FIFTH | 2.0                       | Г |

| CR-55/U         | HC-18/U | ±.005                                  | -55 TO +105                     | SERIES | THIRD | 2.0                       |   |

| CR-56A/U        | HC-18/U | ±.005                                  | -55 TO +105                     | SERIES | FIFTH | 2.0                       | Г |

| CR-59A/U        | HC-18/U | ±.002                                  | +80 TO +90                      | SERIES | FIFTH | 1.0                       | Г |

| CR-60A/U        | HC-18/U | ±.005                                  | -55 TO +105                     | SERIES | FUND  | 5.0                       |   |

| CR-61/U         | HC-18/U | ±.002                                  | +80 TO +90                      | SERIES | THIRD | 1:8 {≶25 MS}              | Г |

| CR-63B/U        | HC-6/U  | 1.01                                   | -40 TO +70                      | 20 PF  | FUND  | 2.0                       | Г |

| CR-64/U         | HC-18/U | ±.005                                  | -55 TO +105                     | 30 PF  | FUND  | 5.0                       | Г |

| CR-65/U         | HC-6/U  | ±.001                                  | +70 TO +80                      | SERIES | THIRD | 2:8 {≶25 MS}              |   |

| CR-66/U         | HC-6/U  | ±.002                                  | -55 TO +105                     | 30 PF  | FUND  | 19:8 (≶18 MS)             |   |

| CR-67/U         | HC-18/U | 1.0025                                 | -55 TO +105                     | SERIES | THIRD | 2.0                       | Г |

| CR-68/U         | HC-6/U  | ±.002                                  | +70 TO +80                      | 32 PF  | FUND  | 5.0                       | Г |

| CR-69A/U        | HC-18/U | ±.002                                  | -55 TO +105                     | 30 PF  | FUND  | 5.0                       | Г |

| CR-71/U         | HC-30/U | ±.00008                                |                                 | 32 PF  | FIFTH | 70 UA                     | Г |

| CR-74/U         | HC-26/U | ±.001                                  | +80 TO +90                      | SERIES | FIFTH | 1.0                       |   |

| CR-75/U         | HC-6/U  | ±.001                                  | +70 TO +80                      | SERIES | FIFTH | 1.0                       | Г |

| CR-76/U         | HC-18/U | ±.0025                                 | -55 TO +105                     | SERIES | THIRD | 2.0                       | Г |

| CR-77/U         | HC-25/U | ±.002                                  | -55 TO +105                     | SERIES | THIRD | 2.0                       |   |

| CR-78/U         | HC-25/U | ±.005                                  | -55 TO +105                     | 30 PF  | FUND  | 5.0                       |   |

| CR-79/U         | HC-25/U | ±.005                                  | -55 TO +105                     | SERIES | FUND  | 5.0                       | Г |

| CR-80/U         | HC-18/U | 1.003                                  | -55 TO +105                     | SERIES | FIFTH | 2.0                       |   |

| CR-81/U         | HC-25/U | 1.005                                  | -55 TO +105                     | SERIES | THIRD | 2.0                       |   |

| CR-82/U         | HC-25/U | ±.005                                  | -55 TO +105                     | SERIES | FIFTH | 2.0                       |   |

| CR-83/U         | HC-25/U | ±.0025                                 | -55 TO +105                     | SERIES | FIFTH | 2.0                       |   |

| CR-84/U         | HC-25/U | 1.002                                  | +80 TO +90                      | SERIES | THIRD | 3:8 (≶35 MS)              |   |

| CR-85/U         | HC-6/U  | 1.0025                                 | -55 TO +105                     | SERIES | FUND  | 18 {≶18 MS}               | Г |

| CR-101/U        | HC-35/U | ±.0025                                 | -55 TO +105                     | 30 PF  | FUND  | 5                         | Г |

| CR-102/U        | HC-35/U | ±.0025                                 | -55 TO +105                     | SERIES | FIFTH | 2                         | Г |

| CR-103/U        | HC-35/U | ±.0025                                 | -55 TO +105                     | SERIES | THIRD | 2                         | Г |

|                 |         |                                        |                                 |        |       |                           | _ |

<sup>\*</sup>FURTHER DETAILS OF THE HOLDERS ARE SHOWN IN FIGURE 5-10.

Table 5-2. (Continued)

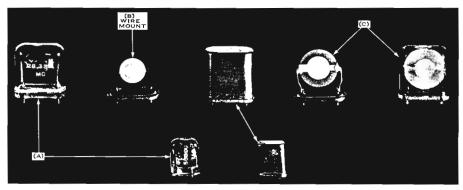

Figure 5-9. Ruggedized crystal mounts.

## 5.11. VIBRATION, SHOCK, AND ACCELERATION

Crystal units are available which will meet most environmental specifications. In general, vibration and shock do not cause catastrophic failures but, rather, frequency shifts and resistance changes. Frequency shifts on the order of 0.0001 percent are common, and resistance changes of 10 percent may occur. Figure 5-9 shows several ruggedized crystal mounts. The wire-mounted crystal is generally not satisfactory for severe environmental conditions, and one of the ruggedized versions must be used. (A) and (C) in Figure 5-9 generally are satisfactory for vibration up to 2000 Hz. Large crystal blanks are difficult to ruggedize and, consequently, low-frequency crystals should be avoided if severe environmental conditions will be encountered. For more specific information on environmental conditions, the reader may consult vibration specifications in MIL-C-3098.\*

### 5.12. STANDARD MILITARY CRYSTALS

It is possible to specify a crystal to fit the needs of a particular oscillator circuit. Where possible, however, it is more desirable to use standard crystals. Table 5-2 presents a summary of selected MIL crystals, while Table 5-3 gives the maximum resistance for these units.

<sup>\*</sup>AT-cut resonators generally show an acceleration sensitivity of about 1 ppb/g. Research is presently being conducted, however, to develop a stress-compensated crystal cut (SC) which shows promise of reducing the sensitivity by more than an order of magnitude. This also results in a reduction of the frequency overshoot during warm up due to thermal stress in the crystal blank.

TABLE 5-3. Maximum Crystal Resistance. (Compiled from MIL-C-3098F, 24 July 1973)

| CR-18A/       | U   | CR-19A/U         |              |  |

|---------------|-----|------------------|--------------|--|

| MHz           | (Ω) | MHz              | (Ω)          |  |

| 0.8 to 0.85   | 625 | 2.6+ to 3        | 90           |  |

| 0.85+ to 0.9  | 600 | 3+ to 3.4        | 70           |  |

| 0.9+ to 1     | 575 | 3.4+ to 3.75     | 52           |  |

| 1+ to 1.12    | 540 | 3.75+ to 4       | 45           |  |

| 1.12+ to 1.25 | 490 | 4+ to 5          | 37           |  |

| 1.25+ to 1.37 | 450 | 5+ to 7          | 25           |  |

| 1.37+ to 1.5  | 410 | 7+ to 10         | 20           |  |

| 1.5+ to 1.62  | 375 | 10+ to 15        | 18           |  |

| 1.62+ to 1.75 | 330 | 15+ to 20        | 15           |  |

| 1.75+ to 1.87 | 300 | CD 254           | / <b>T</b> T |  |

| 1.87+ to 2    | 290 | CR-25A           |              |  |

| 2+ to 2.12    | 270 | kHz              | (Ω)          |  |

| 2.12+ to 2.25 | 245 | 200 to 225       | 2,500        |  |

| 2.25+ to 2.6  | 195 | 225+ to 265      | 3,000        |  |

| 2.6+ to 3     | 150 | 265+ to 290      | 3,500        |  |

| 3+ to 3.4     | 110 | 290+ to 330      | 4,000        |  |

| 3.4+ to 3.75  | 90  | 330+ to 370      | 4,500        |  |

| 3.75+ to 4    | 75  | 370+ to 410      | 5,000        |  |

| 4+ to 5       | 60  | 410+ to 425      | 5,500        |  |

| 5+ to 7       | 35  | 425+ to 460      | 6,500        |  |

| 7+ to 10      | 24  | 460+ to 500      | 7,500        |  |

| 10+ to 15     | 22  | CR-26A/U         |              |  |

| 15+ to 20     | 20  | Same as CR-25A/U | J            |  |

| CR-19A/       |     | CR-27A           | /U           |  |

| MHz           | (Ω) | MHz              | $(\Omega)$   |  |

| 0.8 to 0.85   | 520 | 0.8 to 0.85      | 620          |  |

| 0.85+ to 0.9  | 480 | 0.85 + to 0.9    | 600          |  |

| 0.9+ to 1     | 440 | 0.9+ to 1        | 570          |  |

| 1+ to 1.12    | 400 | 1+ to 1.12       | 540          |  |

| 1.12+ to 1.25 | 380 | 1.12+ to 1.25    | 490          |  |

| 1.25+ to 1.37 | 340 | 1.25+ to 1.37    | 450          |  |

| 1.37+ to 1.5  | 300 | 1.37+ to 1.5     | 410          |  |

| 1.5+ to 1.62  | 275 | 1.5+ to 1.62     | 370          |  |

| 1.62+ to 1.75 | 250 | 1.62+ to 1.75    | 330          |  |

| 1.75+ to 1.87 | 220 | 1.75+ to 1.87    | 300          |  |

| 1.87+ to 2    | 185 | 1.87+ to 2       | 290          |  |

| 2+ to 2.12    | 165 | 2+ to 2.12       | 270          |  |

| 2.12+ to 2.25 | 150 | 2.12+ to 2.25    | 240          |  |

| 2.25+ to 2.6  | 125 | 2.25 + to 2.6    | 190          |  |

TABLE 5-3. (Continued)

| CR-27A/U        |            | CR-50A/U    |            |  |

|-----------------|------------|-------------|------------|--|

| MHz             | $(\Omega)$ | kHz         | $(\Omega)$ |  |

| 2.6+ to 3       | 150        | 16 to 30    | 100,000    |  |

| 3+ to 3.4       | 110        | 30+ to 50   | 90,000     |  |

| 3.4+ to 3.75    | 90         | 50+ to 70   | 80,000     |  |

| 3.75 to 4       | 75         | 70+ to 90   | 70,000     |  |

| 4+ to 5         | 60         | 90+ to 100  | 60,000     |  |

| 5+ to 7         | 35         | CR-52A/U    | 40 Ω       |  |

| 7+ to 10        | 24         |             |            |  |

| 10+ to 15       | 22         |             |            |  |

| 15+ to 20       | 20         | CR-54       | •          |  |

| CR-28A/U        |            | MHz         | <u>(Ω)</u> |  |

| Same as CR-19A/ | ľU         | 50 to 90    | 50         |  |

| CR-35A/U        | <u></u>    | 90+ to 125  | 60         |  |

| Same as CR-19A/ | /U         | CR-55/U     | 40 Ω       |  |

| CR-36A/U        |            | CR-56A/U    | 60 Ω       |  |

| Same as CR-27A/ | /U         |             |            |  |

| CR-37A/U        |            | CR-59A/U    |            |  |

| kHz             | (Ω)        | MHz         | $(\Omega)$ |  |

| 90 to 170       | 5,000      | 50 to 500   | 50         |  |

| 170+ to 250     | 5,500      | 100+ to 125 | 60         |  |

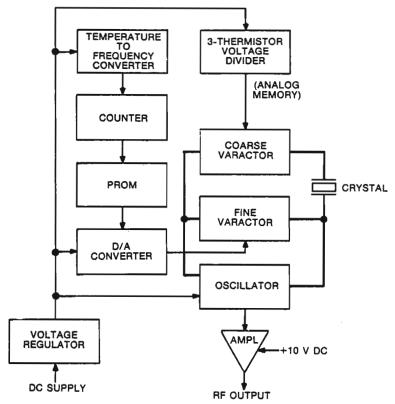

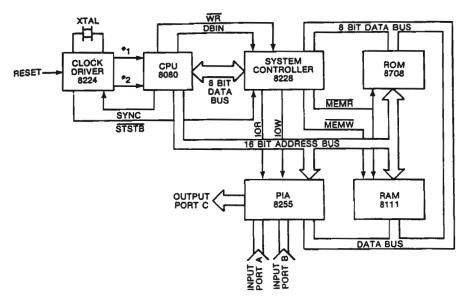

| CR-38A          | \/U        | CR-60A/U    |            |  |